Section: New Software and Platforms

HILECOP

High Level hardware Component Programming

Functional Description

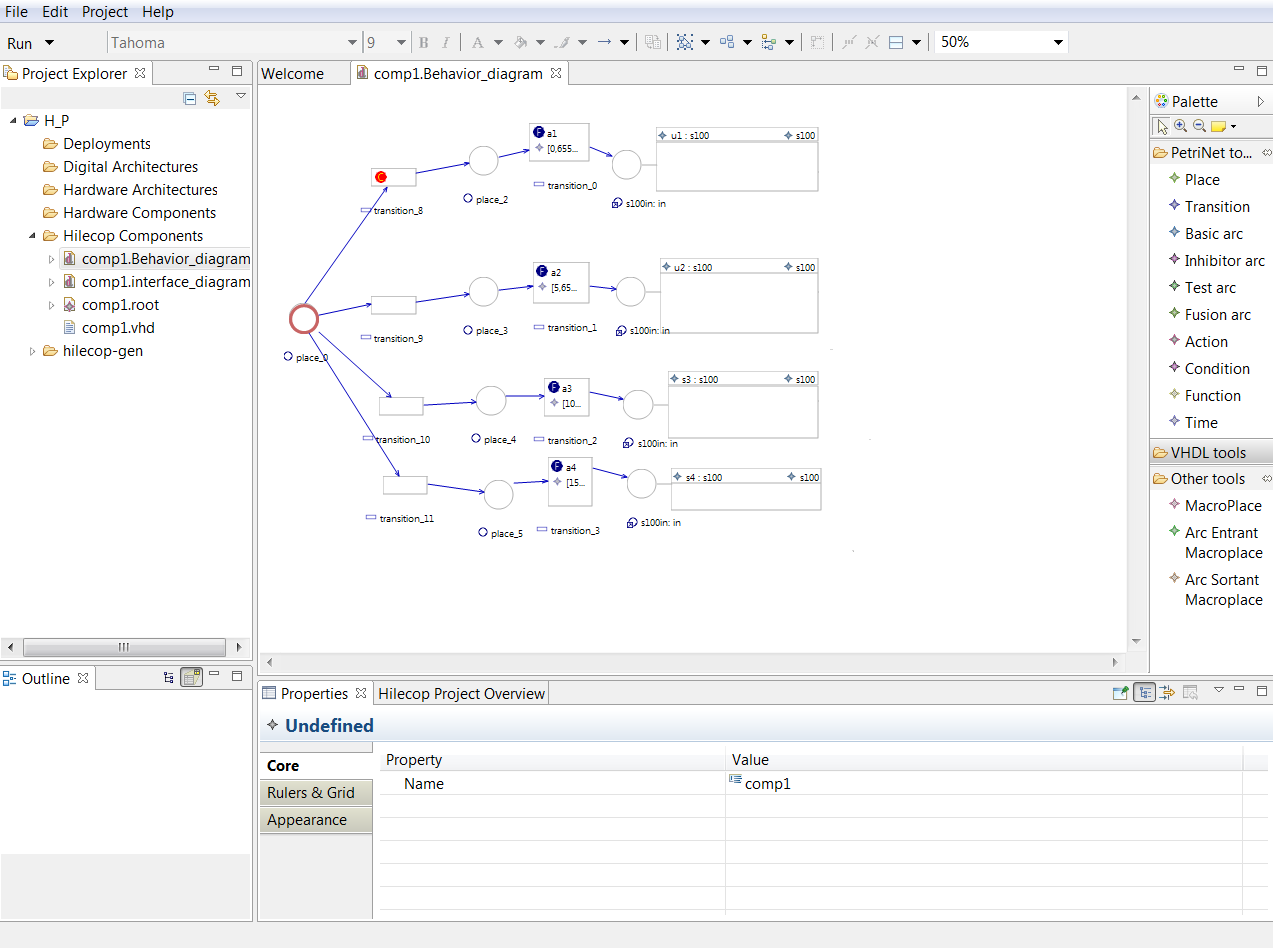

Our SENIS (Stimulation Electrique Neurale dIStribuee) based FES architecture relies on distributed stimulation units (DSU) which are interconnected by means of a 2-wire based network. A DSU is a complex digital system since its embeds among others a dedicated processor (micro-machine with a specific reduced instruction set), a monitoring module and a 3-layer protocol stack. To face the complexity of the units digital part and to ease its prototyping on programmable digital devices (e.g. FPGA), we developed an approach for high level hardware component programming (HILECOP). To support the modularity and the reusability of sub-parts of complex hardware systems, the HILECOP methodology is based on components. An HILECOP component has: a Petri Net (PN) based behavior (fig.2 ), a set of functions whose execution is controlled by the PN, and a set of variables and signals. Its interface contains places and transitions from which its PN model can be inter-connected as well as signals it exports or imports. The interconnection of those components, from a behavioral point out view, consists in the interconnection of places and/or transitions according to well-defined mechanisms: interconnection by means of oriented arcs or by means of the "merging" operator (existing for both places and transitions).

The Eclipse-based version of HILECOP (registered at the french Agence de Protection des Programmes (APP)) has been refactored: for instance, the application ECore model, a new Eclipse E4 architecture and a set of new features (new link types and new views to connect components) have been developed.

Undergoing work concerns the integration, in the HILECOP tool, of the formalism evolutions that allow behavior agregation as well as exception handling, both for analysis and implementation sides.

Specification of GALS systems (Globally Asynchronous Locally Synchronous) is also an ongoing work, the aim being to take into account deployment properties like connecting different clocks to HILECOP components within a same FPGA, or on a set of interconnected FPGAs (and thus interconnecting them by means of asynchronous signals).